Fifo Depth 2j2m2a

This document was ed by and they confirmed that they have the permission to share it. If you are author or own the copyright of this book, please report to us by using this report form. Report 3b7i

Overview 3e4r5l

& View Fifo Depth as PDF for free.

More details w3441

- Words: 1,190

- Pages: 6

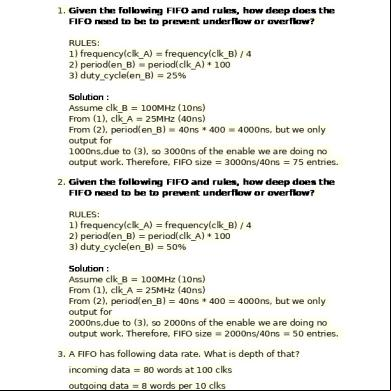

FIFO Depth Calculations 1. Given the following FIFO and rules, how deep does the FIFO need to be to prevent underflow or overflow? RULES: 1) frequency(clk_A) = frequency(clk_B) / 4 2) period(en_B) = period(clk_A) * 100 3) duty_cycle(en_B) = 25% Solution : Assume clk_B = 100MHz (10ns) From (1), clk_A = 25MHz (40ns) From (2), period(en_B) = 40ns * 400 = 4000ns, but we only output for 1000ns,due to (3), so 3000ns of the enable we are doing no output work. Therefore, FIFO size = 3000ns/40ns = 75 entries. 2. Given the following FIFO and rules, how deep does the FIFO need to be to prevent underflow or overflow? RULES: 1) frequency(clk_A) = frequency(clk_B) / 4 2) period(en_B) = period(clk_A) * 100 3) duty_cycle(en_B) = 50% Solution : Assume clk_B = 100MHz (10ns) From (1), clk_A = 25MHz (40ns) From (2), period(en_B) = 40ns * 400 = 4000ns, but we only output for 2000ns,due to (3), so 2000ns of the enable we are doing no output work. Therefore, FIFO size = 2000ns/40ns = 50 entries. 3. A FIFO has following data rate. What is depth of that? incoming data = 80 words at 100 clks outgoing data = 8 words per 10 clks

read clk = write clk fifo data width = 1 word. Solution : 40. 4. Suppose 200 bytes burst is to be written at 100 MHZ, 1 byte per write clock. and Read clock is 50 MHZ, 1 byte read per read clock. what is the FIFO depth? Solution : Time taken to write 1 byte = (1/100) = 10 ns So, Time taken to write 200 Bytes = 10 * 200 = 2000 ns Time required to read 1 byte = (1/50) = 20 ns So, in 2000 ns date bytes read = (2000/20) = 100 Bytes So, FIFO Depth = 200 - 100 = 100 Bytes. 5. Suppose 125 bytes burst is to be written at 100 MHZ, 4 byte per write clock. and Read clock is 50 MHZ, 2 byte read per read clock. what is the FIFO depth? Solution : Time taken to write 4 byte = (4/100) Mhz = 40 ns So, Time taken to write 125 Bytes = (40 * 125)/4 = 1250 ns Time required to read 2 byte = (2/50) = 40 ns So, in 5000 ns date bytes read = (5000/40) /2 = 62.5 = 63 Bytes So, FIFO Depth = 125 - 63 = 62 Bytes. 6. Consider the case of a FIFO where the 'Fw' is 100 MHz and 50 words are written into the FIFO in 100 clocks while the 'Fr' is 50 MHz and one word is read out every clock. Solution : In the worst case scenario, the 50 words are written into the FIFO as a burst in 500 ns. In the same time duration, the read side can read only 25 words out of the FIFO. The remaining 25 words are read out of the FIFO in the 50 idle write clocks. So

the depth of the FIFO should be at least 28. (Three clock cycles are for synchronizer latency). 7. Assume that Write Clock Frequency WClk = 200 Mhz Read Clock Frequency RClk = 100 Mhz No of data per 100 WClk cycle (Data rate including delay) = 80 data Solution : So WClk = 200Mhz = 5ns RClk = 100 Mhz = 10ns Total Time Taken for writing 80 data = 80*5 = 400ns . But Time Taken for reading 80 data = 80*10 = 800 ns . So difference b/w data write & read same no of data = 800 -400 = 400 ns . ie we want to store 400ns data to some position. Otherwise data will over write . How many data will write this 400ns time = 400ns/5ns = 80 . We have to store this 80 Data . So we can say that FIFO should have minimum depth of 80 . 8. Assume that Write Clock Frequency WClk = 200 Mhz Read Clock Frequency RClk = 300 Mhz No of data per 200 WClk cycle (Data rate including delay) = 100 data Solution : So WClk = 200Mhz = 5ns RClk = 300 Mhz = 3.3ns Total Time Taken for writing 100 data = 100*5 = 500ns . But Time Taken for reading 100 data = 100*3.3 = 330 ns .

So difference b/w data write & read Same no of data = 500 -330 = 170 ns. i.e. we want to store 170 ns data to some position. Otherwise data will over write. How many data will write this 170ns time = 170ns/5ns = 34. We have to store this 34 Data. So we can say that FIFO should have minimum depth of 34. 9. Assume that we have to design a FIFO with following requirements and We want to calculate minumum FIFO depth, A synchronized fifo Writing clock 30MHz - F1 Reading clock 40MHz - F2 Writing Burst Size - B Case 1: There is 1 idle clock cycle for reading side - I Case 2: There is 10 idle clock cycle for reading side - I FIFO depth calculation = B - B *F2/(F1*I) If we have alternate read cycle i.e between two read cycle there is IDLE cycle. FIFO depth calculation = B - B * F2/(F1*2) In our present problem FIFO depth = B - B *40/(30*2) = B(1-2/3) = B/3 That means if our Burst amount of data is 10, FIFO DEPTH = 10/3 = 3.333 = 4 (approximatly) If B = 20 FIFO depth = 20/3 = 6.6 = 7 or 8 (clocks are asynchronous)

If B = 30 FIFO depth = 30/3 = 10 10+1 = 11 (clocks are asynchronous) If 10 IDLE cycles betweeen two read cycles . FIFO DEPTH = B - B *F2/(F1*10) . = B(1-4/30) = B * 26 /30 10. Assume that we have to design a FIFO with following requirements and We want to calculate minumum FIFO depth, A synchronized fifo Writing clock 50MHz - F1 Reading clock 200MHz - F2 Writing Burst Size - 40 There is 20 idle clock cycle for reading side - I FIFO depth calculation = B - B *F2/(F1*I) In our present problem FIFO depth = 40 - 40 *200/(50*20) = 40 – (40*0.2) = 32

11.

Write Clk Freq = 60 MHz.

Read Clk Freq = 100 MHz. Maximum Write Burst Size = 1024. Delay between writes in burst = 4 clk. Read Delay = 2 clk. Solution : In our present problem FIFO depth = 1024 - 1024 *(100*2) / (60*4)

= 1024 – (1024*0.833) = 171.008 ~ 171

12.

Write Clk Freq = 60 MHz.

Read Clk Freq = 100 MHz. Maximum Write Burst Size = 1024. Delay between writes in burst = 4 clk. Depth = 171 Calculate maximum Read Delay allowable so that fifo will not under flow Solution : FIFO depth calculation = B - B *F2/(F1*Rd_delay) In our present problem FIFO depth = 1024 - 1024 *100/ (60*rd_delay) 171 = 1024 – (1706.67 / read_delay ) Read_dealy = 1706.67 / 853 = 2.0007 ~ 2 clock cycles.

read clk = write clk fifo data width = 1 word. Solution : 40. 4. Suppose 200 bytes burst is to be written at 100 MHZ, 1 byte per write clock. and Read clock is 50 MHZ, 1 byte read per read clock. what is the FIFO depth? Solution : Time taken to write 1 byte = (1/100) = 10 ns So, Time taken to write 200 Bytes = 10 * 200 = 2000 ns Time required to read 1 byte = (1/50) = 20 ns So, in 2000 ns date bytes read = (2000/20) = 100 Bytes So, FIFO Depth = 200 - 100 = 100 Bytes. 5. Suppose 125 bytes burst is to be written at 100 MHZ, 4 byte per write clock. and Read clock is 50 MHZ, 2 byte read per read clock. what is the FIFO depth? Solution : Time taken to write 4 byte = (4/100) Mhz = 40 ns So, Time taken to write 125 Bytes = (40 * 125)/4 = 1250 ns Time required to read 2 byte = (2/50) = 40 ns So, in 5000 ns date bytes read = (5000/40) /2 = 62.5 = 63 Bytes So, FIFO Depth = 125 - 63 = 62 Bytes. 6. Consider the case of a FIFO where the 'Fw' is 100 MHz and 50 words are written into the FIFO in 100 clocks while the 'Fr' is 50 MHz and one word is read out every clock. Solution : In the worst case scenario, the 50 words are written into the FIFO as a burst in 500 ns. In the same time duration, the read side can read only 25 words out of the FIFO. The remaining 25 words are read out of the FIFO in the 50 idle write clocks. So

the depth of the FIFO should be at least 28. (Three clock cycles are for synchronizer latency). 7. Assume that Write Clock Frequency WClk = 200 Mhz Read Clock Frequency RClk = 100 Mhz No of data per 100 WClk cycle (Data rate including delay) = 80 data Solution : So WClk = 200Mhz = 5ns RClk = 100 Mhz = 10ns Total Time Taken for writing 80 data = 80*5 = 400ns . But Time Taken for reading 80 data = 80*10 = 800 ns . So difference b/w data write & read same no of data = 800 -400 = 400 ns . ie we want to store 400ns data to some position. Otherwise data will over write . How many data will write this 400ns time = 400ns/5ns = 80 . We have to store this 80 Data . So we can say that FIFO should have minimum depth of 80 . 8. Assume that Write Clock Frequency WClk = 200 Mhz Read Clock Frequency RClk = 300 Mhz No of data per 200 WClk cycle (Data rate including delay) = 100 data Solution : So WClk = 200Mhz = 5ns RClk = 300 Mhz = 3.3ns Total Time Taken for writing 100 data = 100*5 = 500ns . But Time Taken for reading 100 data = 100*3.3 = 330 ns .

So difference b/w data write & read Same no of data = 500 -330 = 170 ns. i.e. we want to store 170 ns data to some position. Otherwise data will over write. How many data will write this 170ns time = 170ns/5ns = 34. We have to store this 34 Data. So we can say that FIFO should have minimum depth of 34. 9. Assume that we have to design a FIFO with following requirements and We want to calculate minumum FIFO depth, A synchronized fifo Writing clock 30MHz - F1 Reading clock 40MHz - F2 Writing Burst Size - B Case 1: There is 1 idle clock cycle for reading side - I Case 2: There is 10 idle clock cycle for reading side - I FIFO depth calculation = B - B *F2/(F1*I) If we have alternate read cycle i.e between two read cycle there is IDLE cycle. FIFO depth calculation = B - B * F2/(F1*2) In our present problem FIFO depth = B - B *40/(30*2) = B(1-2/3) = B/3 That means if our Burst amount of data is 10, FIFO DEPTH = 10/3 = 3.333 = 4 (approximatly) If B = 20 FIFO depth = 20/3 = 6.6 = 7 or 8 (clocks are asynchronous)

If B = 30 FIFO depth = 30/3 = 10 10+1 = 11 (clocks are asynchronous) If 10 IDLE cycles betweeen two read cycles . FIFO DEPTH = B - B *F2/(F1*10) . = B(1-4/30) = B * 26 /30 10. Assume that we have to design a FIFO with following requirements and We want to calculate minumum FIFO depth, A synchronized fifo Writing clock 50MHz - F1 Reading clock 200MHz - F2 Writing Burst Size - 40 There is 20 idle clock cycle for reading side - I FIFO depth calculation = B - B *F2/(F1*I) In our present problem FIFO depth = 40 - 40 *200/(50*20) = 40 – (40*0.2) = 32

11.

Write Clk Freq = 60 MHz.

Read Clk Freq = 100 MHz. Maximum Write Burst Size = 1024. Delay between writes in burst = 4 clk. Read Delay = 2 clk. Solution : In our present problem FIFO depth = 1024 - 1024 *(100*2) / (60*4)

= 1024 – (1024*0.833) = 171.008 ~ 171

12.

Write Clk Freq = 60 MHz.

Read Clk Freq = 100 MHz. Maximum Write Burst Size = 1024. Delay between writes in burst = 4 clk. Depth = 171 Calculate maximum Read Delay allowable so that fifo will not under flow Solution : FIFO depth calculation = B - B *F2/(F1*Rd_delay) In our present problem FIFO depth = 1024 - 1024 *100/ (60*rd_delay) 171 = 1024 – (1706.67 / read_delay ) Read_dealy = 1706.67 / 853 = 2.0007 ~ 2 clock cycles.