Modelsim Manual 2a446n

This document was ed by and they confirmed that they have the permission to share it. If you are author or own the copyright of this book, please report to us by using this report form. Report 3b7i

Overview 3e4r5l

& View Modelsim Manual as PDF for free.

More details w3441

- Words: 1,967

- Pages: 35

Tutorial: ModelSim version MentorGraphics Versión de estudiante (limitada a 10.000 lineas, inactivas varias funcionalidades, no se pueden mezclar lenguajes, restringido a VHDL y Verilog, …. )

La versión con la que se ha realizado este tutorial es la 10.4a

1 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Índice -Antes de empezar el diseño -Flujos de trabajo -Arranque de la herramienta -Librerías iníciales -Estructura de las ventanas -Pasos para realizar la simulación -1) Crear un proyecto -2) Compilar -3) simular -Tareas a realizar 2 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Antes de empezar - Crearse

una carpeta (Mux_sintesis), y llevarse alli los ficheros con los que se vaya a trabajar (bajarselos de Moodle) Importante: la ruta donde está la carpeta donde se va a trabajar no debe tener blancos ni acentos - Por ejemplo INFORMÁTICA INDUSTRIAL no serviría

3 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

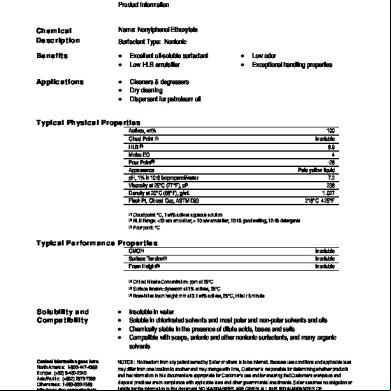

Antes de empezar: Fichero: mux_bus.vhd

•Entidad y arquitectura de mux2:1 •Las entradas son vectores de num_bits •Los datos son binarios sin signo del paquete NUMERIC_STD

4 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Antes de empezar: Fichero: mux_bus.vhd LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.NUMERIC_STD.all;

•Entidad y arquitectura de mux2:1 •Las entradas son vectores de num_bits •Los datos son binarios sin signo del paquete NUMERIC_STD

ENTITY mux_bus IS GENERIC (num_bits : IN POSITIVE); PORT ( control: IN STD_LOGIC; data_in0, data_in1: IN UNSIGNED ((num_bits - 1) DOWNTO 0); data_out: OUT UNSIGNED((num_bits - 1) DOWNTO 0) ); END mux_bus; ARCHITECTURE simple OF mux_bus IS BEGIN data_out <= data_in0 WHEN control = '0' ELSE data_in1; END simple;

5 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Antes de empezar: Fichero: mux_bus_tb.vhd (1) LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.all; USE IEEE.NUMERIC_STD.all;

Entidad y arquitectura para test

-- Entidad para test ENTITY test_mux_bus IS END test_mux_bus; -- Arquitectura para test ARCHITECTURE test_mux_bus_arq of test_mux_bus IS -- Parte declarativa -- Declaración de componentes COMPONENT mux_bus IS GENERIC (num_bits : IN POSITIVE:= 3); PORT (control: IN STD_LOGIC; data_in0, data_in1: IN UNSIGNED ((num_bits - 1) DOWNTO 0); data_out: OUT UNSIGNED((num_bits - 1) DOWNTO 0)); END COMPONENT; 6 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Antes de empezar: Fichero: mux_bus_tb.vhd (2) -- Declaración de señales auxiliares CONSTANT ciclo: TIME := 10 ns; -- para sincronizar la generación de señales SIGNAL selector_entrada: STD_LOGIC:= '0';-- se inicializa a 0 para que arranque la --

secuencia NOT

SIGNAL dato_entrada0,dato_entrada1 : UNSIGNED (2 DOWNTO 0); SIGNAL salida: UNSIGNED (2 DOWNTO 0); -- Comienzo de la arquitectura BEGIN selector_entrada <= NOT selector_entrada AFTER ciclo/2; -- la señal cambia cada ½ -ciclo -- Conexionado de los puertos del componente con las señales de entrada U1: mux_bus GENERIC MAP (num_bits => 3) PORT MAP (control => selector_entrada, data_in0 => dato_entrada0, data_in1 => dato_entrada1, data_out => salida);

7 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Antes de empezar: Fichero: mux_bus_tb.vhd (3) -- Generación de los datos de entrada “cero” en UNSIGNED con 3 bits (valores ascendentes)

PROCESS BEGIN FOR i IN 0 TO 7 LOOP dato_entrada0 <= TO_UNSIGNED (i,3); -- convierte el valor de i a 3 bits WAIT FOR ciclo; -- espera un tiempo = definido en ciclo END LOOP; END PROCESS; -- Generación de los datos de entrada “uno”en UNSIGNED con 3 bits (valores descendentes)

PROCESS BEGIN FOR j IN 7 DOWNTO 0 LOOP dato_entrada1 <= TO_UNSIGNED (j,3); -- convierte el valor de j a 3 bits WAIT FOR ciclo; -- espera un tiempo = ciclo END LOOP; END PROCESS; END test_mux_bus_arq; 8 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Flujos de trabajo Flujo básico de simulación para trabajar con distintas librerias

Flujo de un proyecto (más facil) No hay que crearse una libreria de trabajo. La crea la herramienta Los proyectos permanecen accesibles cuando la herramienta está abierta a no ser que se cierren explicitamente

9 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Arranque de la herramienta

10 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Librerias iniciales

11 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Estructura de las ventanas La vista de las ventanas se puede personalizar en VIEW

12 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 1. Crear proyecto

Seleccionado por el , es conveniente que sea el mismo que la entidad más alta de la jerarquia Donde estan ubicados los ficheros fuente

Crea la libreria WORK 13 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 1. Crear proyecto – Añadiendo ficheros

14 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 2. Compilar un diseño - Opciones Funciones de compilación

15 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 2. Compilar un diseño – Opciones Si no se añaden los ficheros al proyecto – se abren desde la carpeta donde estan ubicados

16 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 2. Compilar un diseño - Opciones Si no se añaden los ficheros al proyecto – se abren desde la carpeta donde estan ubicados

17 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 2. Compilar un diseño – Resultados en WORK

Si hay errores de compilacion no incluye las unidades de diseño en la libreria WORK

18 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 3. Simular – Seleccionar el diseño

Seleccionando el fichero desde la pestaña de simulación o bien haciendo doble clic sobre él en la libreria work 19 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 3. Simular – Ventanas informativas

Objetos – Constantes variables, señales, nets Jerarquia del diseño

Procesos – Sentencias concurrentes 20 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 3. Simular – Ventanas informativas

21 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 3. Simular –

Abrir una ventana para las ondas

22 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 3. Simular – Añadir ondas a visualizar

Se debe seleccionar de que item se quieren visualizar las ondas 23 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 3. Simular – Añadir ondas a visualizar Efecto de incluir todas los items del diseño

24 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 3. Simular – Añadir ondas a visualizar Efecto incluyendo las señales una a una

25 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 3. Simular –

Seleccionar las condiciones de simulación

Hemos incrementado el valor por defecto de 100 ns a 200 ns

26 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 3. Simular –

Ejecutar la simulacion

Ejecuta la simulacion durante 100 ns

Ejecuta la simulación durante el periodo seleccionado

27 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 3. Simular –

Visualización de resultados

Para que se activen las funcionalidades de las ondas hay que desanclar la ventana

28 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 3. Simular –

Visualización de resultados

UTILIZACION DEL ZOOM

29 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 3. Simular –

Visualización de resultados ZOOM

30 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 3. Simular –

Visualización de resultados Formatos de visualización

-- Generación de los datos de entrada “cero” en UNSIGNED con 3 bits (valores ascendentes) PROCESS BEGIN FOR i IN 0 TO 7 LOOP dato_entrada0 <= TO_UNSIGNED (i,3); -- convierte el valor de i a 3 bits WAIT FOR ciclo; -- espera un tiempo = ciclo END LOOP; END PROCESS;

31 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 3. Simular –

Visualización de resultados

Se añaden más cursores

Click con boton izquierdo para avanzar el cursor 32 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

3. Simular –

Visualización de resultados

Se cambian las propiedades del grid

Para medir la diferencia entre dos cursores se bloquea uno de ellos se pone en rojo y marca el valor

33 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 3. Simular –

Visualización de resultados

34 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Tareas a realizar - Sobre los ficheros mux_bus.vhd, mux_bus_tb.vhd, realizar las siguientes modificaciones: a) b) c) d)

Cambiar el número de bits de las entradas del MUX a 4 bits Los valores de la señal dato_entrada0 seran descendentes de 15 a 0 Los valores de la señal dato_entrada1 seran ascendentes de 0 a 15 El periodo de la señal selector_entrada sera de 8 ns

-

Simular con ModelSim durante un tiempo de 300 ns

-

Entrega de la captura de pantalla en Moodle

35 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

La versión con la que se ha realizado este tutorial es la 10.4a

1 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Índice -Antes de empezar el diseño -Flujos de trabajo -Arranque de la herramienta -Librerías iníciales -Estructura de las ventanas -Pasos para realizar la simulación -1) Crear un proyecto -2) Compilar -3) simular -Tareas a realizar 2 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Antes de empezar - Crearse

una carpeta (Mux_sintesis), y llevarse alli los ficheros con los que se vaya a trabajar (bajarselos de Moodle) Importante: la ruta donde está la carpeta donde se va a trabajar no debe tener blancos ni acentos - Por ejemplo INFORMÁTICA INDUSTRIAL no serviría

3 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Antes de empezar: Fichero: mux_bus.vhd

•Entidad y arquitectura de mux2:1 •Las entradas son vectores de num_bits •Los datos son binarios sin signo del paquete NUMERIC_STD

4 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Antes de empezar: Fichero: mux_bus.vhd LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.NUMERIC_STD.all;

•Entidad y arquitectura de mux2:1 •Las entradas son vectores de num_bits •Los datos son binarios sin signo del paquete NUMERIC_STD

ENTITY mux_bus IS GENERIC (num_bits : IN POSITIVE); PORT ( control: IN STD_LOGIC; data_in0, data_in1: IN UNSIGNED ((num_bits - 1) DOWNTO 0); data_out: OUT UNSIGNED((num_bits - 1) DOWNTO 0) ); END mux_bus; ARCHITECTURE simple OF mux_bus IS BEGIN data_out <= data_in0 WHEN control = '0' ELSE data_in1; END simple;

5 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Antes de empezar: Fichero: mux_bus_tb.vhd (1) LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.all; USE IEEE.NUMERIC_STD.all;

Entidad y arquitectura para test

-- Entidad para test ENTITY test_mux_bus IS END test_mux_bus; -- Arquitectura para test ARCHITECTURE test_mux_bus_arq of test_mux_bus IS -- Parte declarativa -- Declaración de componentes COMPONENT mux_bus IS GENERIC (num_bits : IN POSITIVE:= 3); PORT (control: IN STD_LOGIC; data_in0, data_in1: IN UNSIGNED ((num_bits - 1) DOWNTO 0); data_out: OUT UNSIGNED((num_bits - 1) DOWNTO 0)); END COMPONENT; 6 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Antes de empezar: Fichero: mux_bus_tb.vhd (2) -- Declaración de señales auxiliares CONSTANT ciclo: TIME := 10 ns; -- para sincronizar la generación de señales SIGNAL selector_entrada: STD_LOGIC:= '0';-- se inicializa a 0 para que arranque la --

secuencia NOT

SIGNAL dato_entrada0,dato_entrada1 : UNSIGNED (2 DOWNTO 0); SIGNAL salida: UNSIGNED (2 DOWNTO 0); -- Comienzo de la arquitectura BEGIN selector_entrada <= NOT selector_entrada AFTER ciclo/2; -- la señal cambia cada ½ -ciclo -- Conexionado de los puertos del componente con las señales de entrada U1: mux_bus GENERIC MAP (num_bits => 3) PORT MAP (control => selector_entrada, data_in0 => dato_entrada0, data_in1 => dato_entrada1, data_out => salida);

7 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Antes de empezar: Fichero: mux_bus_tb.vhd (3) -- Generación de los datos de entrada “cero” en UNSIGNED con 3 bits (valores ascendentes)

PROCESS BEGIN FOR i IN 0 TO 7 LOOP dato_entrada0 <= TO_UNSIGNED (i,3); -- convierte el valor de i a 3 bits WAIT FOR ciclo; -- espera un tiempo = definido en ciclo END LOOP; END PROCESS; -- Generación de los datos de entrada “uno”en UNSIGNED con 3 bits (valores descendentes)

PROCESS BEGIN FOR j IN 7 DOWNTO 0 LOOP dato_entrada1 <= TO_UNSIGNED (j,3); -- convierte el valor de j a 3 bits WAIT FOR ciclo; -- espera un tiempo = ciclo END LOOP; END PROCESS; END test_mux_bus_arq; 8 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Flujos de trabajo Flujo básico de simulación para trabajar con distintas librerias

Flujo de un proyecto (más facil) No hay que crearse una libreria de trabajo. La crea la herramienta Los proyectos permanecen accesibles cuando la herramienta está abierta a no ser que se cierren explicitamente

9 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Arranque de la herramienta

10 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Librerias iniciales

11 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Estructura de las ventanas La vista de las ventanas se puede personalizar en VIEW

12 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 1. Crear proyecto

Seleccionado por el , es conveniente que sea el mismo que la entidad más alta de la jerarquia Donde estan ubicados los ficheros fuente

Crea la libreria WORK 13 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 1. Crear proyecto – Añadiendo ficheros

14 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 2. Compilar un diseño - Opciones Funciones de compilación

15 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 2. Compilar un diseño – Opciones Si no se añaden los ficheros al proyecto – se abren desde la carpeta donde estan ubicados

16 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 2. Compilar un diseño - Opciones Si no se añaden los ficheros al proyecto – se abren desde la carpeta donde estan ubicados

17 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 2. Compilar un diseño – Resultados en WORK

Si hay errores de compilacion no incluye las unidades de diseño en la libreria WORK

18 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 3. Simular – Seleccionar el diseño

Seleccionando el fichero desde la pestaña de simulación o bien haciendo doble clic sobre él en la libreria work 19 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 3. Simular – Ventanas informativas

Objetos – Constantes variables, señales, nets Jerarquia del diseño

Procesos – Sentencias concurrentes 20 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 3. Simular – Ventanas informativas

21 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 3. Simular –

Abrir una ventana para las ondas

22 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 3. Simular – Añadir ondas a visualizar

Se debe seleccionar de que item se quieren visualizar las ondas 23 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 3. Simular – Añadir ondas a visualizar Efecto de incluir todas los items del diseño

24 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 3. Simular – Añadir ondas a visualizar Efecto incluyendo las señales una a una

25 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 3. Simular –

Seleccionar las condiciones de simulación

Hemos incrementado el valor por defecto de 100 ns a 200 ns

26 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 3. Simular –

Ejecutar la simulacion

Ejecuta la simulacion durante 100 ns

Ejecuta la simulación durante el periodo seleccionado

27 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 3. Simular –

Visualización de resultados

Para que se activen las funcionalidades de las ondas hay que desanclar la ventana

28 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 3. Simular –

Visualización de resultados

UTILIZACION DEL ZOOM

29 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 3. Simular –

Visualización de resultados ZOOM

30 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 3. Simular –

Visualización de resultados Formatos de visualización

-- Generación de los datos de entrada “cero” en UNSIGNED con 3 bits (valores ascendentes) PROCESS BEGIN FOR i IN 0 TO 7 LOOP dato_entrada0 <= TO_UNSIGNED (i,3); -- convierte el valor de i a 3 bits WAIT FOR ciclo; -- espera un tiempo = ciclo END LOOP; END PROCESS;

31 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 3. Simular –

Visualización de resultados

Se añaden más cursores

Click con boton izquierdo para avanzar el cursor 32 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

3. Simular –

Visualización de resultados

Se cambian las propiedades del grid

Para medir la diferencia entre dos cursores se bloquea uno de ellos se pone en rojo y marca el valor

33 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Pasos: 3. Simular –

Visualización de resultados

34 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid

Tareas a realizar - Sobre los ficheros mux_bus.vhd, mux_bus_tb.vhd, realizar las siguientes modificaciones: a) b) c) d)

Cambiar el número de bits de las entradas del MUX a 4 bits Los valores de la señal dato_entrada0 seran descendentes de 15 a 0 Los valores de la señal dato_entrada1 seran ascendentes de 0 a 15 El periodo de la señal selector_entrada sera de 8 ns

-

Simular con ModelSim durante un tiempo de 300 ns

-

Entrega de la captura de pantalla en Moodle

35 © Grupo de Tecnología de Computadores.- V. Rodellar Departamento de Arquitectura y Tecnología de Sistemas Informátic Facultad de Informática – Universidad Politécnica de Madrid